### UNIVERSITY of CALIFORNIA Santa Barbara

# Automated Reasoning for Agile and Robust Chip Design

A Dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Computer Science

by

Zachary David Sisco

### Committee in Charge:

Professor Ben Hardekopf, Co-Chair Professor Jonathan Balkind, Co-Chair Professor Timothy Sherwood Professor Zachary Tatlock, University of Washington

| The Dissertation of Zachary David Sisco is approved. |

|------------------------------------------------------|

|                                                      |

|                                                      |

| Professor Timothy Sherwood                           |

| Professor Zachary Tatlock, University of Washington  |

| Professor Jonathan Balkind, Committee Co-Chair       |

| Professor Ben Hardekopf, Committee Co-Chair          |

### Automated Reasoning for Agile and Robust Chip Design

Copyright © 2025

by

Zachary David Sisco

### **DEDICATION**

To my parents and brothers.

To Linda and Eric for the Thanksgivings away from home.

To Jeremy for the good jams.

To Drew, we'll make that game someday.

To Pingyuan for your love and support.

### Acknowledgements

I cannot enumerate all of the people—mentors, mentees, colleagues, and more—who helped me in carrying out the research in this dissertation. I could not have done it alone. There are a few I would like to specially thank:

**Ben Hardekopf** For guiding me through this research and helping me hone my writing and teaching skills.

**Jonathan Balkind** For jumping in with us on this wild idea called "hardware decompilation," and staying on! Over the years you have been an invaluable mentor in research and navigating my academic career, nudging me towards many opportunities to engage with folks in the PL–Hardware community.

**Tim Sherwood** For your enthusiasm and openness to applying esoteric ideas to computer architecture, and for giving me an opportunity to teach about those ideas.

**Adam Bryant** For introducing me to computer science research, and giving me the chance to work with some smart folks at Galois.

**Harlan Kringen** For countless hours of shop talk and for being a good friend. Your deep wells of PL theory knowledge are inexhaustible and yet somehow all trace back to the 1970s. You have shared so much excellent music which has become the soundtrack to my PhD.

**Andrew Alex** For jumping onto the OWL project and braving the jungle of parentheses that is its Racket codebase.

**Thanawat Techaumnuaiwit** For trying (and nearly succeeding) to make me a better developer by showing me better tools (though I'm still not using Nix).

**Gus Smith** For inviting me to give a talk at the UW PLSE lab that eventually kicked off a collaboration over our shared research areas.

The UCSB PL Lab To the senior members: Mehmet Emre, Michael Christensen, and Lawton Nichols for welcoming me into the lab. And to the current members: Harlan Kringen, Jingtao Xia, Hitomi Nakayama, Peter Boyland, and Sarah Canto. I've enjoyed sharing the lab with you all.

The UCSB Arch Lab For helping me understand what a computer is and how we build them. And also for organizing fun events outside of the lab. A special thank you to the folks in the lab (current and former) who I have collaborated with: Zechen Ma, Boming Kong, Yeganeh Aghamohammadi, Pranjali Jain, and Sijie Kong.

### Curriculum Vitæ Zachary David Sisco

#### **Education**

| 2025 | Ph.D. in Computer Science, University of California, Santa Barbara. |

|------|---------------------------------------------------------------------|

| 2018 | M.S. in Computer Science, Wright State University.                  |

| 2014 | B.S. in Mathematics, Ohio University.                               |

#### **Publications**

- **Z. D. Sisco**, A. D. Alex, Z. Ma, Y. Aghamohammadi, B. Kong, B. Darnell, T. Sherwood, B. Hardekopf, and J. Balkind. Control Logic Synthesis: Drawing the Rest of the OWL. In *Architectural Support for Programming Languages and Operating Systems, Volume 4 (AS-PLOS)*. 2024.

- G. H. Smith, **Z. D. Sisco**, T. Techaumnuaiwit, J. Xia, V. Canumalla, A. Cheung, Z. Tatlock, C. Nandi, and J. Balkind. There and Back Again: A Netlist's Tale With Much Egraphin'. *Workshop on Languages, Tools, and Techniques for Accelerator Design (LATTE)*. 2024.

- **Z. D. Sisco**, J. Balkind, T. Sherwood, and B. Hardekopf. Loop Rerolling For Hardware Decompilation. In *Programming Language Design and Implementation (PLDI)*. 2023.

- H. Kringen, **Z. D. Sisco**, J. Balkind, T. Sherwood, and B. Hardekopf. Semi-Automated Translation of a Formal ISA Specification to Hardware. *Programming Languages for Architecture (PLARCH)*. 2023.

- **Z. D. Sisco**, J. Balkind, T. Sherwood, and B. Hardekopf. A Position on Program Synthesis for Processor Development. *Workshop on Languages, Tools, and Techniques for Accelerator Design (LATTE)*. 2022.

- **Z. D. Sisco**, A. R. Bryant. A Semantics-Based Approach to Concept Assignment in Assembly Code. *International Conference on Cyber Warfare and Security (ICCWS)*. 2017.

- **Z. D. Sisco**, P. P. Dudenhofer, A. R. Bryant. Modeling Information Flow for an Autonomous Agent to Support Reverse Engineering Work. *Journal of Defense Modeling and Simulation*. 2017.

#### **Awards**

- 2024 PhD Student of the Year, Computer Science Department, UCSB.

- 2024 Neal Fenzi Resonant Founder Fellowship, Resonant, Inc.

- 2022 2nd Place Award, ACM SIGPLAN PLDI Student Research Competition.

### Experience

| 2024–2025   | Computing Fellow, College of Creative Studies, UCSB. |

|-------------|------------------------------------------------------|

| Summer 2024 | Research Mentor, Research Mentorship Program, UCSB.  |

| Summer 2023 | Intern, Galois, Inc.                                 |

| 2020–2023   | Research Assistant, UCSB.                            |

| 2016–2018   | Research Assistant, Wright State University.         |

| 2013-2016   | Programmer Analyst, Motorists Insurance Group.       |

### **Teaching – Instructor of Record**

| Spring 2025 | UCSB CMPTG 130E: Exploring the Hardware–Software Interface. |

|-------------|-------------------------------------------------------------|

| Winter 2025 | UCSB CMPTG 1L: Programming Laboratory.                      |

| Summer 2024 | UCSB CS 9: Intermediate Python Programming.                 |

| Fall 2022   | UCSB CS 32: Object-Oriented Design & Implementation.        |

| Summer 2022 | UCSB CS 24: Problem Solving with Computers II.              |

| Summer 2021 | UCSB CS 16: Problem Solving with Computers I.               |

| Winter 2021 | UCSB CS 16: Problem Solving with Computers I.               |

| Summer 2020 | UCSB CS 138: Automata & Formal Languages.                   |

### **Teaching – Lead Teaching Assistant**

| Fall 2023 | UCSB CS 501: Techniques of Computer Science Teaching. |

|-----------|-------------------------------------------------------|

| Fall 2022 | UCSB CS 501: Techniques of Computer Science Teaching. |

### **Teaching – Teaching Assistant**

| Fall 2024   | UCSB CMPTG 1L: Programming Laboratory.              |

|-------------|-----------------------------------------------------|

| Winter 2023 | UCSB CS 154: Computer Architecture.                 |

| Spring 2020 | UCSB CS 138: Automata & Formal Languages.           |

| Winter 2020 | UCSB CS 56: Advanced Applications Programming.      |

| Fall 2019   | UCSB CS 56: Advanced Applications Programming.      |

| Fall 2017   | WSU CS 7830: Machine Learning.                      |

| Fall 2017   | WSU CS 4350: Operating System Internals and Design. |

#### **Abstract**

### Automated Reasoning for Agile and Robust Chip Design

by

#### Zachary David Sisco

Modern chip design embodies enormous complexity, from general-purpose processors to specialized hardware accelerators. With the trend towards specialization, chip designers need techniques that let them quickly iterate over a design while fitting into familiar programming languages and tools. However, designing a chip with speed and robustness remains a challenge. Chip design requires reasoning between different layers of abstraction, however these tools do not provide mechanisms to connect specifications with implementations to ensure correctness. Programming languages for chip design rely on technology-specific components, but lack helpful abstractions needed to support common deployment platforms, making it difficult to adapt and compose designs. And further, the design ecosystem is fragmented between systems and tool chains without the ability to interoperate.

This thesis presents my research on improving chip design tools with automated reasoning techniques. I use program synthesis techniques to bridge the gap between an architectural specification and a low-level hardware implementation, developing a new technique called *control logic synthesis*. I establish a new field called *hardware decompilation*, which is about lifting common hardware artifacts to high-level source code, enabling design transpilation and automating the effort of re-targeting designs to different technologies. And finally, to address challenges with technology constraints, I developed a memory design language that uses equational reasoning techniques to automatically target multiple memory technologies from a single interface. Through

the application of these automated reasoning techniques, I opened two wholly new areas in the chip design space enabling novel design processes that were not possible before, improving developer agility and design verifiability.

# **Contents**

| Cı         | arricu             | ılum Vitae                             | vii  |

|------------|--------------------|----------------------------------------|------|

| <b>A</b> l | bstrac             | et e e e e e e e e e e e e e e e e e e | ix   |

| Li         | st of              | Figures                                | xiii |

| Li         | st of              | Tables                                 | xv   |

| 1          | Intr<br>1.1<br>1.2 | oduction Thesis Statement              |      |

| 2          | Con                | trol Logic Synthesis                   | 5    |

|            | 2.1                | Introduction                           | 5    |

|            | 2.2                | Background                             | 9    |

|            | 2.3                | Control Logic Synthesis Technique      | 15   |

|            | 2.4                | Case Studies                           |      |

|            | 2.5                | Evaluation                             |      |

|            | 2.6                | Related work                           |      |

|            | 2.7                | Conclusion                             | 45   |

| 3          | Loo                | p Rerolling for Hardware Decompilation | 47   |

|            | 3.1                | Introduction                           | 47   |

|            | 3.2                | The Maki Intermediate Language         |      |

|            | 3.3                | Loop Identification                    |      |

|            | 3.4                | Sketch Generation for Loop Rerolling   |      |

|            | 3.5                | Program Synthesis for Loop Rerolling   | 68   |

|            | 3.6                | Evaluation                             |      |

|            | 3.7                | Related Work                           |      |

|            | 3.8                | Conclusion                             | 86   |

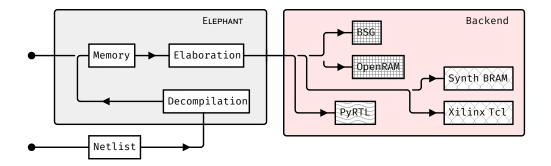

| 4  | $\mathbf{A} \mathbf{M}$ | lemory Design Language for Automated Memory Mapping | 87 |

|----|-------------------------|-----------------------------------------------------|----|

|    | 4.1                     | Introduction                                        | 37 |

|    | 4.2                     | Background                                          | 90 |

|    | 4.3                     | ELEPHANT for Automated Memory Technology Mapping    | 94 |

|    | 4.4                     | Memory Decompilation                                | )4 |

|    | 4.5                     | Evaluation                                          | 12 |

|    | 4.6                     | Related Work                                        | 21 |

|    | 4.7                     | Conclusion                                          | 24 |

| 5  | Con                     | clusions                                            | 25 |

| Bi | bliog                   | raphy 12                                            | 27 |

# **List of Figures**

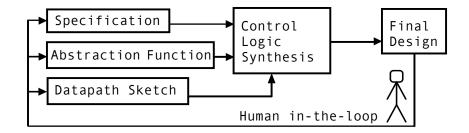

| 2.1  | An overview of the control logic synthesis technique                      | 6  |

|------|---------------------------------------------------------------------------|----|

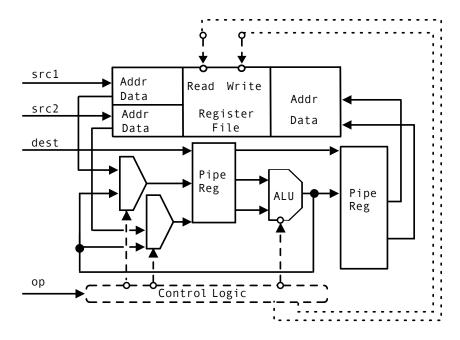

| 2.2  | The datapath diagram for a three-stage implementation of the ALU ma-      | 10 |

| 2.0  | chine                                                                     | 12 |

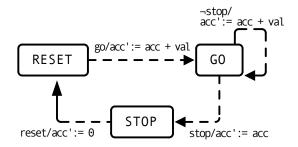

| 2.3  | An FSM for the accumulator machine                                        | 14 |

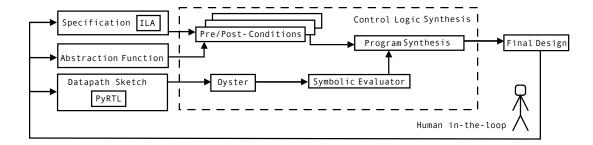

| 2.4  | A diagram of the overall control logic synthesis workflow                 | 15 |

| 2.5  | The grammar for Oyster                                                    | 17 |

| 2.6  | An algorithm for combining individual control logic synthesis results     |    |

|      | together into a complete implementation                                   | 25 |

| 2.7  | PyRTL code of the generated control logic for a load word instruction     |    |

|      | (LW) in the RV32I core                                                    | 32 |

| 2.8  | The grammar for ILA decode and update expressions                         | 38 |

| 3.1  | An accumulator circuit instantiated with a 4-bit ripple-carry adder writ- |    |

|      | ten in SystemVerilog                                                      | 50 |

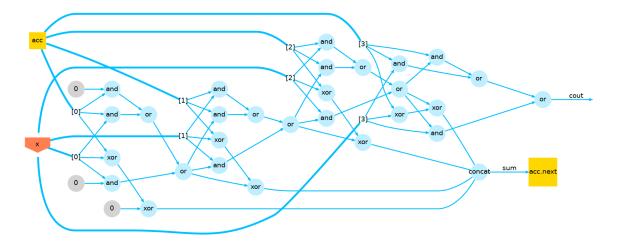

| 3.2  | Graph representation of a netlist for a 4-bit accumulator                 | 52 |

| 3.3  | The grammar for Maki                                                      | 54 |

| 3.4  | A selection of big-step structural operational semantics for Maki         | 56 |

| 3.5  | Maki representation of the 4-bit accumulator netlist                      | 58 |

| 3.6  | A tokenized version of the 4-bit accumulator netlist                      | 60 |

| 3.7  | Intermediate reroll sketches of an accumulator design in Maki             | 63 |

| 3.8  | Final reroll sketch of the accumulator design, and the rerolled designed  |    |

|      | after program synthesis                                                   | 68 |

| 3.9  | Decompiled SystemVerilog (a) and PyRTL (b) code for the 4-bit accu-       |    |

|      | mulator                                                                   | 71 |

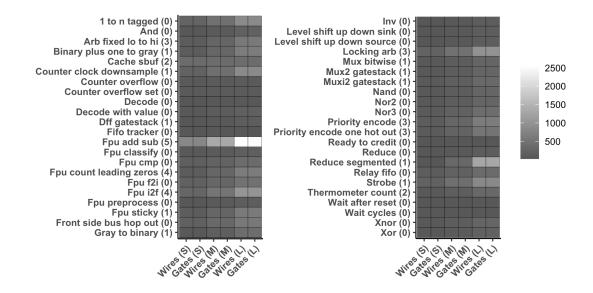

| 3.10 | Heat map of benchmark sizes for the BaseJump modules                      | 74 |

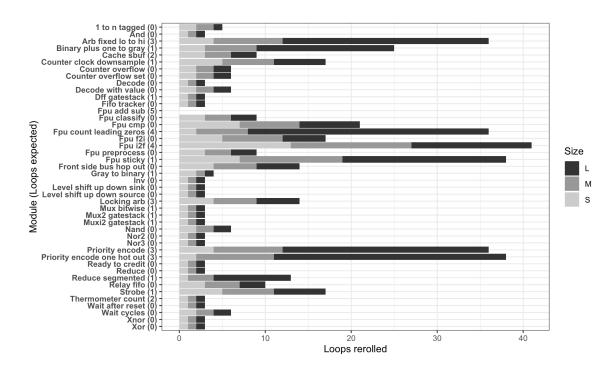

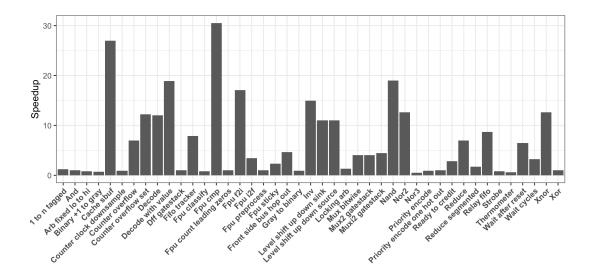

|      | Number of loops rerolled across all BaseJump benchmarks                   | 77 |

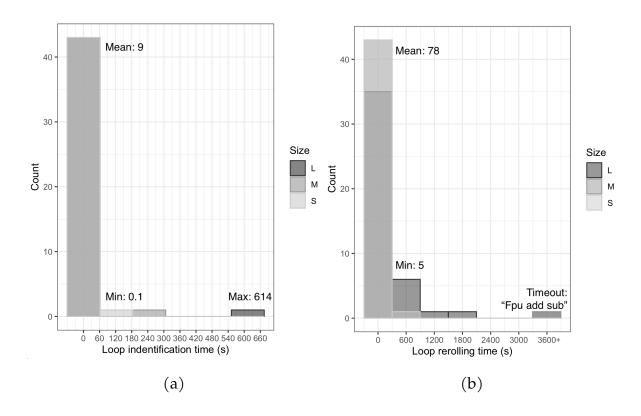

|      | Histograms of loop identification and rerolling performance               | 80 |

|      | Speedups in Verilator simulation times across all "large" versions of the |    |

|      | BaseJump STL modules                                                      | 82 |

| 4.1  | An illustration of manual memory technology mapping                       | 88 |

|      | , 0, 11 0                                                                 |    |

| 4.2 | The grammar for Elephant and a selection of type signatures       | 95  |

|-----|-------------------------------------------------------------------|-----|

| 4.3 | The core elaboration rules for Elephant                           | 97  |

| 4.4 | An illustration of the Elephant tool flow                         | 113 |

| 4.5 | Original PyRTL implementation of the data memory, including write |     |

|     | masking logic, for a RISC-V core                                  | 116 |

# **List of Tables**

| 2.1 | Control logic synthesis results over all case studies 40                |

|-----|-------------------------------------------------------------------------|

| 2.2 | Size of designs with generated control logic compared to a hand-written |

|     | reference implementation                                                |

| 3.1 | PyRTL benchmark information                                             |

| 3.2 | PyRTL benchmark loop identification and rerolling results               |

| 4.1 | Memory mapping validation tests from Elephant across a range of port    |

|     | configurations                                                          |

| 4.2 | Memory decompilation results                                            |

|     | Large-scale case studies from OPDB                                      |

| 4.4 | BlackParrot memory decompilation results                                |

# Chapter 1

# Introduction

The cost of designing new, specialized chips for emerging applications is too high, with industry studies showing roughly half of development time is spent on verification [1]. To handle the growing complexity of specialized hardware as well as enabling newcomers to the space with smaller teams and resources, we need new approaches to address the current state-of-the-art in hardware development. However, modern hardware description languages (HDLs) and electronic design automation tools have not kept pace with the demands brought by the "golden age" of computer architecture [2]. In this thesis, I address three challenges that hamper developer agility and verifiability during the chip design process:

**Multilevel Reasoning** The current system-on-chip (SoC) development process suffers from decoupling between all of the layers of abstraction. Enormous effort goes into verification between the specifications, models, and implementation—the difficulty being the semantic gap between these layers. Further, verification during this process is inherently *post hoc*: designers write microarchitectural models, *then* verify; developers write RTL code, *then* verify. This disjointed process leads to long design

Introduction Chapter 1

iterations, hindering agility and increasing verification burden.

Interoperability The growth of new HDLs and open-source hardware design tools adds new features that improve the process of designing hardware over legacy languages and proprietary tools. However, these new languages and tools often lack the ability the interoperate, fragmenting the communities that use them and making migration difficult, as manual porting is impractical. Limited interoperability means that new HDLs cannot leverage the vast body of existing designs written in legacy languages, and existing designs cannot take advantage of the new features provided by these modern tools.

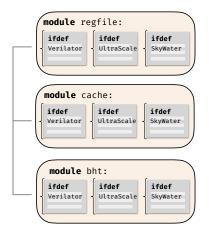

**Technology Constraints** Languages and tools for chip design rely on technology-specific components, but lack helpful abstractions needed to support common deployment platforms, making it difficult to adapt and compose designs. Targeting platforms, such as ASIC and FPGA, requires technology-specific code and so each new technology being targeted requires updating an existing part of the code with multiple independent descriptions of the same component.

The recognition of these three challenges facing chip design brings me to my thesis statement:

### 1.1 Thesis Statement

The integration of automated-reasoning techniques, such as constraint solvers and equational reasoning, into programming languages used for hardware design improves developer agility and verifiability.

In this thesis, I will show how these techniques enable new hardware design pro-

Introduction Chapter 1

cesses via automated verification and program synthesis, overcoming design challenges related to multilevel reasoning, interoperability, and technology constraints.

### 1.2 Organization of this Document

The following describes the organization of this thesis:

Chapter 2 To address the first challenge, *multilevel reasoning*, I adapt program synthesis techniques to languages used for chip design, bridging the gap between an architectural formal specification and a low-level hardware implementation, automating the programming of tedious and error-prone control logic. This technique, called **Control Logic Synthesis**, allows designers to quickly iterate over chips designs, focusing on the critical design questions without getting bogged down in low-level details of control. It is based on work published in ASPLOS 2024 [3], and LATTE 2022 [4]. This work was done in collaboration with Andrew David Alex, Zechen Ma, Yeganeh Aghamohammadi, Boming Kong, Benjamin Darnell, Timothy Sherwood, Ben Hardekopf, and Jonathan Balkind. Specifically, Andrew David Alex contributed the compiler to generate Rosette code from ILA specifications, the AES accelerator benchmark, as well as writing. Zechen Ma, Yeganeh Aghamohammadi, Boming Kong, and Benjamin Darnell contributed in benchmark development and case study evaluation.

**Chapter 3** To address the *interoperability* challenge, I established a new field called **Hardware Decompilation**, which is about lifting gate-level netlists to high-level code in hardware description languages. In this work, I apply advanced program synthesis and compiler techniques to the hardware domain. This work enables transpiling designs from one language to another, automates the effort of re-targeting designs to

Introduction Chapter 1

different technologies, and speeds up analyses over gate-level netlists. It is based on work published in PLDI 2023 [5], and supported by the National Science Foundation under Grants No. 2006542, 1763699, 1717779.

**Chapter 4** To address the *technology constraints* challenge, I developed a **Memory De**sign Language which includes a rich memory abstraction that automatically targets many technologies from a single interface. From this memory abstraction, I show how we can build a compiler for memories as well as a decompiler for memories from netlists—both based on the same formalized rule set. In this work I use powerful equational reasoning techniques normally used in software compilers enabling automated memory technology targeting, making designs more robust and reusable. The memory decompiler is a continued exploration of hardware decompilation established in Chapter 3. It is based on work that has been submitted to a conference and is currently under revision. I am the first author on this work, and my co-authors are Sijie Kong, Daniel Ruelas-Petrisko, Jingtao Xia, Julian Springer, Varun Rao, Spencer Wang, Gus Henry Smith, Ben Hardekopf, and Jonathan Balkind. In particular, Sijie Kong made significant contributions to the implementation for the memory decompiler as well as the dynamic programming algorithm for memory mapping with technology constraints. Daniel Ruelas-Petrisko helped with the BlackParrot case study and its evaluation, as well as XCI ingestion. Jingtao Xia, Julian Springer, and Varun Rao contributed parts of the memory compilation and decompilation implementation. Spencer Wang contributed to the evaluation, validating memory mapping results. Gus Henry Smith contributed writing about equality saturation as well as development of the abstract memory formalization.

# Chapter 2

# **Control Logic Synthesis**

### 2.1 Introduction

Embedded SoCs are the foundation of some of our most critical infrastructure, controlling everything from remote surgical equipment [6], to telecommunications satellites [7], to access to other larger compute and storage resources [8]. In such domains, any correctness issue could be catastrophic. To reduce cost and meet the growing demand for specialised hardware, we must find opportunities for correct-by-construction automation of design. Our new technique, control logic synthesis, meets this goal by freeing design engineers from writing control logic.

In this chapter, we describe a method for automatically generating correct by construction control logic for embedded-class root-of-trust SoCs. Our technique generates control logic with respect to a formal instruction set architecture (ISA) or instruction-level abstraction (ILA) specification, with only a minimal microarchitectural model, leaving the hardware designer free to iterate over the datapath and specification. Despite the leakiness of the control-datapath abstraction, we find that the datapath captures the designer's *intent* and narrows the innumerable microarchitectural possibili-

Figure 2.1: An overview of our technique: starting from an HDL sketch of the datapath combined with a formal architectural specification to generate correct-by-construction HDL code that completes the control logic.

ties down to a more manageable set tailored to the most important behaviors.

We work to compose the problem in a way that is tractable for modern program synthesis tools (synthesizing from the entire design and specification fails even for small hardware designs) and to handle the disconnect between the architectural specification and the microarchitecture (pipelining being one example challenge). We focus on the kinds of bespoke embedded SoC designs which current solver-aided techniques can handle and where correctness is crucial.

### 2.1.1 The Control-Datapath Divide

Traditionally, embedded SoC design requires human reasoning about all of the behaviors a specific ISA/ILA might embody, down through the microarchitecture, including optimizations such as pipelining, caching, etc., to a complete digital design. Holding such a complex set of relationships in one's head all at once is incredibly difficult. When adopting an existing, open design, today's hardware designer must learn all of this information to extend the architecture and optimise the microarchitecture for their domain-specific goals. To make our reasoning simpler, it is common to divide a design roughly between a *datapath* (the composition of functional units that operate on

data and stateful elements) and the *control logic* (the signals that coordinate and route data through appropriate functional units at appropriate times). Designers typically concentrate first on instructions' computational action as they independently traverse these datapaths, leaving their exact orchestration of control for later.

Of course, the control-datapath divide is imperfect as the interactions between them and their relation to the ISA semantics can be subtle and difficult to reason about, particularly for a new or unfamiliar designer. In practice, data flows between the control and datapaths bidirectionally, thanks to matters like data-dependent control flow. Even worse, as the designer iteratively changes either the architecture (e.g., adding custom instructions) or the datapath (e.g., functional units or microarchitectural optimizations) they must reconsider all of these interdependencies which can easily cause pervasive and non-local changes to the control logic.

These problems are further exacerbated by the fact that testing is the most common means for assessing an SoC design's correctness (particularly in small, agile teams). While formal verification techniques are adopted in industry [9, 10, 11, 12, 13, 14, 15, 16, 17], they usually involve manually creating a separate, detailed microarchitectural model that must be updated in lockstep with the design. In contrast, our correct-by-construction approach requires only a lightweight microarchitectural model to handle optimizations such as pipelining in the form of a programmatic mapping from architectural state to microarchitectural components.

### 2.1.2 Technique Overview

Figure 2.1 gives a high-level overview of our technique: the hardware developer provides (1) the datapath in a Hardware Description Language (HDL); (2) the architectural specification that the hardware implements, taken from existing formaliza-

tions such as ILA [18, 19, 20, 21, 22, 23] or Sail [24]; and (3) the lightweight model connecting the datapath components to the specification, in the form of an abstraction function. Our method takes those inputs and uses program synthesis techniques adapted from the Programming Languages community to automatically create the necessary control logic, thus completing the hardware design (datapath + control logic) and ensuring correctness against the specification. Control logic synthesis enables hardware developers to freely modify and iterate in design of both the ISA/ILA and the datapath without getting caught up in the abstruse details of control. Further, it assures that the final implementation (not just a model of the design) is correct.

We focus our efforts on the design space exemplified by OpenTitan [8] (an open source silicon Root-of-Trust): embedded-class, small, but sophisticated designs for applications requiring bespoke, highly trusted cores and accelerators (e.g., for cryptography). We first target the core RISC-V ISA plus cryptography extensions and investigate both pipelined and non-pipelined microarchitectures. Further, to demonstrate our technique's generality, we generate control logic for a bespoke constant-time cryptography core and also for a cryptographic accelerator targeting the Advanced Encryption Standard (AES). Our major contributions are:

- We introduce a novel HDL Intermediate Representation (IR) named Oyster designed to be amenable to HDL-level program synthesis techniques (Section 2.3.1).

- We present an HDL program synthesis toolchain¹ that takes a datapath and a specification for ISA/ILA semantics and automatically generates HDL code that implements the control logic (Section 2.3).

- We evaluate our toolchain on an embedded-class root-of-trust SoC design, encompassing a RISC-V core, constant-time cryptography core, and AES hardware

<sup>&</sup>lt;sup>1</sup>Available as a free and open-source artifact: https://github.com/UCSBarchlab/owl

accelerator, automatically extracting semantics from architectural specifications written in ILA [19], and generating correct-by-construction control logic code in the Python-based HDL PyRTL [25].

## 2.2 Background

Here we briefly review the concept of the control-datapath divide in hardware design and make clear specifically how we split control and datapath for the class of designs we consider. We broadly define the datapath as "the functional units that define system operations"; and control logic as "the signals that coordinate and route data through the appropriate functional units at the appropriate times." While in practice the line between control and data can be blurry, to focus the scope of our control logic synthesis technique we describe two control structures commonly found in hardware designs: (1) instruction decoders, and (2) finite state machines (FSMs). For this purpose we present small but illustrative examples of hardware designs with each type of structure and show how we split each design into control logic and datapath.

#### 2.2.1 Instruction-Level Abstraction

In this work, we use ILA for architectural specifications. We provide an overview of ILA here to aid in understanding our example use cases and direct the reader to the ILA paper [19] for a complete description. ILA provides a mechanism to functionally specify the hardware-software interface for both processors and accelerators. As the name implies, the core unit of computation is modeled as an "instruction." Instruction models capture the software-visible state updates made per unit of computation. Each instruction is specified with functions describing how it is fetched, decoded, and how it updates state. ILA authors specify each instruction's fetch, decode, and up-

date functionality with the help of the ILA C++ library. In the case of a processor, the instruction model is the familiar concept of an ISA instruction specification. ILA abstracts this further by allowing the specification to rely on a wide-range of state-variables and inputs that are not present in general-purpose ISA specifications, but are widely used in MMIO-based accelerators. For example, one may want to trigger an instruction only when certain criteria in its state and input values are met. ILA also allows breaking down complex instruction into a hierarchy of smaller state updates, which further enables reasoning about and specifying complex device interfaces.

### 2.2.2 Instruction Decoder Example

A common control structure is instruction decoder-style control logic. This type of control receives an instruction or opcode as input and, based on decode logic from the specification, sets control signals to route data through the design to correctly execute the given operation. Consider the following ILA specification for an ALU machine:

```

ilang::Ila CreateAluIla() {

auto ila = ilang::Ila("alu_ila");

// args here are name and bitwidth

auto op = ila.NewBvInput("op", 2);

auto dest = ila.NewBvInput("dest", 2);

auto src1 = ila.NewBvInput("src1", 2);

auto src2 = ila.NewBvInput("src2", 2);

// name, addr width, data width

auto regs = ila.NewMemState("regs", 2, 8);

auto rs1_val = ilang::Load(regs, src1);

auto rs2_val = ilang::Load(regs, src2);

```

```

auto ADD = ila.NewInstr("ADD");

{

ADD.SetDecode(op == BvConst(1, 2));

auto res = rs1_val + rs2_val;

ADD.SetUpdate(regs, ilang::Store(regs, dest, res));

}

// similar for other ALU operations ...

return ila; }

```

The ALU takes four inputs (op, src1, src2, and dest), which are previously decoded from some instruction. The architectural state is made of four registers stored in regs. SetDecode is an ILA method that specifies the conditional logic to determine whether an instruction is enabled to execute. The decode logic for an ADD operation in the ALU specification states that the op input must be equal to 01. Similarly, SetUpdate describes the actual state update logic for the instruction. SetUpdate operates on one state element at a time; its first argument is the given state element, and the second argument is an expression describing how to update the state. For the ADD operation, the update procedure updates register file regs using the built-in ILA function ilang::Store which stores a new value in memory state.

Suppose the hardware designer wants to implement the ALU machine as a three-stage pipeline; then Figure 2.2 illustrates the design diagram, clearly labeling which part of the design corresponds to the control logic (with the bulk of the design being the datapath). The hardware designer has inserted two pipeline registers in the datapath, one after reading the src1 and src2 registers from the register file and one for storing the result of the ALU operation. The dashed boxes and arrows indicate where the designer would place the control logic to guide the data through the datapath and to select certain paths and functionality depending on the op input. Given the datapath

Figure 2.2: The datapath diagram for a three-stage implementation of the ALU machine. The decoded instruction is input to the control unit, which determines how to set control signals in the datapath.

ath portion of this diagram and a specification for the desired behavior, our technique would automatically infer the correct control logic to fulfill the intended system behavior.

### 2.2.3 Finite State Machine Example

Another common class of control logic we consider are FSMs. Consider a simple accumulator machine with the following specification, expressed in ILA:

```

ilang::Ila CreateAccIla() {

auto ila = ilang::Ila("acc_ila");

// args are name and bitwidth

auto reset = ila.NewBvInput("reset", 1);

```

```

auto go = ila.NewBvInput("go", 1);

auto stop = ila.NewBvInput("stop", 1);

auto val = ila.NewBvInput("val", 2);

auto acc = ila.NewBvState("acc", 8);

auto state = ila.NewBvState("state", 2);

auto reset_instr = ila.NewInstr("reset_instr");

reset_instr.SetDecode(state == STOP && reset == 1);

reset_instr.SetUpdate(acc, 0);

reset_instr.SetUpdate(state, RESET)

auto go_instr = ila.NewInstr("go_instr");

go_instr.SetDecode((state == RESET && go == 1) || (state == GO && stop == 0));

go_instr.SetUpdate(acc, acc + val);

reset_instr.SetUpdate(state, G0)

auto stop_instr = ila.NewInstr("stop_instr");

stop_instr.SetDecode(state == GO && stop == 1);

stop_instr.SetUpdate(acc, acc);

return ila; }

```

The specification describes a design with state acc, and three instructions that update the state based on the input signals (reset, go, and stop).

Suppose the hardware designer intends to implement an FSM (illustrated in Figure 2.3) that matches the accumulator specification. The FSM has three states for the accumulator updates associated with the reset, go, and stop inputs; it defines transitions between the three states with predicates derived from those input signals.

In this case, the datapath is simply the set of FSM states and the control logic is the transitions between them. Given the accumulator updates required for each state as

Figure 2.3: An FSM for the accumulator machine. Each state corresponds to how the machine updates the accumulator register. The input signals, reset, go, and stop predicate the state transitions. Control logic synthesis generates the parts of the design indicated in the dotted lines, including the transition logic.

well as the specification, our technique would automatically infer the necessary state encodings, transition conditions, and FSM transitions to fulfill the intended system behavior.

One implementation of the datapath, expressed in pseudocode, looks as follows:

```

state := ??

with state:

?? → acc := 0

?? → acc := acc + val

?? → acc := acc

out := acc

```

The ?? in the code represents control points in the datapath. The with statement is syntactic sugar for conditional assignment predicated on the state argument; it describes the conditional updates in the datapath to the accumulator (here the designer implements acc as a register).

The key point is that our control logic synthesis technique only requires a datapath sketch (the solid-line components of Figures 2.2 and 2.3) and a specification. Control

Figure 2.4: A diagram of the overall control logic synthesis workflow.

logic synthesis fills in the rest of the design—i.e., all of the dotted-lines in Figures 2.2 and 2.3 and their associated logic.

### 2.3 Control Logic Synthesis Technique

In this section we describe the high-level process to automatically generate correctby-construction control logic. We show through our case studies in Section 2.4 how to specialize it to common architectures and hardware designs.

Figure 2.4 presents the overall work-flow of our toolchain. The inputs are (1) an architectural specification using ILA [19]; (2) an HDL sketch of the datapath<sup>2</sup>; and (3) a lightweight abstraction function mapping state in the datapath sketch to the architectural specification level. Our tool automatically extracts correctness conditions from the ILA specification plus the abstraction function; translates the datapath sketch into an intermediate representation called Oyster; and finally, via Rosette [26, 27], compiles the Oyster program and correctness conditions together into a symbolic form to generate the control logic. A human can then iterate on the design by modifying the specification and/or the datapath sketch (and updating the abstraction function accordingly) to get new designs.

<sup>&</sup>lt;sup>2</sup>Specified using the PyRTL HDL [25], though other languages such as SystemVerilog could be supported.

The control logic synthesis process comprises three main components, detailed in the following subsections:

- 1. An intermediate representation (IR) tailored for program synthesis (Section 2.3.1) that captures essential datapath constructs as well as holes for control logic.

- 2. An abstraction function between the microarchitecture of the datapath sketch and architectural specification (Section 2.3.2), serving as a lightweight microarchitectural model which connects architectural state in the datapath to state in the specification.

- 3. And finally, a program synthesis technique that fills the holes in the datapath sketch using the pre- and postconditions from the formal architectural specification as constraints, generating correct-by-construction control logic (Section 2.3.3).

### 2.3.1 Oyster Intermediate Representation

Our representation must be amenable to automated reasoning and also easily constructed from conventional HDLs. We present an IR named Oyster that is high-level enough to easily translate to/from HDLs such as PyRTL and Verilog yet is also designed to accommodate program synthesis. Oyster embodies a subset of features from conventional HDLs in order to reduce the complexity of automated reasoning while still being complete enough to express non-trivial designs (as shown in our case studies). Oyster programs can be translated to SMT constraints expressed in the theories of bitvectors and uninterpreted functions which allows us to leverage standard program synthesis techniques and tools.

Figure 2.5 describes the grammar for Oyster. An Oyster program has two components: (1) a set of declarations for inputs, outputs, and stateful elements, and (2) a

```

Design ::= \operatorname{decl}(\operatorname{decl}^+) \operatorname{stmt}^+

\operatorname{decl} \in \operatorname{Declaration} ::= \operatorname{input} \operatorname{name} \operatorname{width} \mid \operatorname{output} \operatorname{name} \operatorname{width}

\mid \operatorname{register} \operatorname{name} \operatorname{width} \mid

\mid \operatorname{hole} \operatorname{name} \operatorname{width} \mid

\operatorname{stmt} \in \operatorname{Statement} ::= \operatorname{var} := \operatorname{expr} \mid \operatorname{write} \operatorname{mem} \operatorname{addr} \operatorname{data} \operatorname{enable}

\operatorname{expr} \in \operatorname{Expression} ::= \operatorname{var} \mid \operatorname{const} \mid \neg \operatorname{expr} \mid \operatorname{expr} \operatorname{binop} \operatorname{expr}

\mid \operatorname{if} \operatorname{expr} \operatorname{then} \operatorname{expr} \operatorname{else} \operatorname{expr}

\mid \operatorname{extract} \operatorname{expr} \operatorname{high} \operatorname{low} \mid \operatorname{read} \operatorname{mem} \operatorname{addr}

\operatorname{const} \in \operatorname{Constant} ::= \operatorname{width} \text{'} \operatorname{value}

\operatorname{binop} \in \operatorname{BinaryOps} ::= \wedge \mid \vee \mid \oplus \mid + \mid =

\operatorname{mem}, \operatorname{name}, \operatorname{var} \in \operatorname{Identifier}

\operatorname{high}, \operatorname{low}, \operatorname{value}, \operatorname{width} \in \operatorname{Integer}

\operatorname{addr}, \operatorname{data}, \operatorname{cond}, \operatorname{enable} \in \operatorname{Expression}

```

Figure 2.5: The grammar for Oyster. An "extract" expression extracts the bits from the bitvector value in expr between the bit-index positions low and high.

series of statements that describe the design, how data flows to its output ports, and how to update stateful elements. Oyster represents all variables as bitvectors, with the exception of memories. We model memories as a pair containing an uninterpreted function for reads and an association list to track writes. For space reasons we do not include here all of the operators supported by Oyster expressions, which include many common bitvector operations.

The **hole** construct in Figure 2.5 allows the hardware designer to specify where the control logic should be filled in for the datapath sketch. Our case studies (Section 2.4) detail how to use holes in datapath sketches for control logic generation in different design scenarios.

An Oyster interpreter is essentially a cycle-accurate simulator for synchronous hardware designs. Thus, we assume that all Oyster designs are synchronous with a single implicit clock—all writes to registers and memory take effect in the next cycle. We implement the Oyster interpreter in Rosette, a Racket-based framework for solver-aided programming. A key feature of Rosette is that by writing a concrete interpreter for a language, Rosette automatically lifts that interpreter to work with symbolic values, thus generating a symbolic interpreter "for free". This symbolic interpreter then leverages SMT solvers to solve satisfiability questions such as those that we will use to automatically generate control logic.

#### 2.3.2 Abstraction Function

We use the abstraction function to map datapath components in Oyster code to architecture-level state in the specification. Because of the semantic gap between the architectural specification and the datapath implementation, it is not obvious to formal reasoning tools (such as a program synthesizer) what the connection is between,

for example, architectural registers in the specification and a register file in the implementation. An abstraction function maps effectful behavior at the specification level (for example, reading and writing to state) into the semantics of the datapath components for a particular microarchitecture. This section describes abstraction functions at a high level, and our case studies in Section 2.4 give more detailed examples.

For an abstraction function, the developer needs to specify for each architectural state element in the specification:

- 1. The corresponding name of the datapath component;

- The type of the datapath component: one of either input, output, register, or memory;

- 3. A list of state effects indicating reads or writes from/to the datapath component, annotated with timing (that is, for each read/write, when the effect occurs in the datapath).

We specify abstraction functions (denoted  $\alpha$ ) for control logic synthesis with the following grammar:

```

\alpha ::= (\mathsf{SpecID} \colon \{\mathsf{name} \colon \mathsf{DatapathID}, \ \mathsf{type} \colon \mathit{type}, \ [\mathit{effect}^+] \})^+ with cycles: TimeStep, \mathit{assume}^* \mathit{type} ::= \mathsf{input} \mid \mathsf{output} \mid \mathsf{register} \mid \mathsf{memory} \mathit{effect} ::= \mathsf{read} \colon \mathsf{TimeStep} \mid \mathsf{write} \colon \mathsf{TimeStep} \mathit{assume} ::= [\mathsf{DatapathID} \colon \mathsf{TimeStep}]^+

```

For the three-stage ALU example in Section 2.2.2, the developer would provide the following abstraction function:

```

op: {name: 'op', type: input, [read: 1]}

src1: {name: 'src1', type: input, [read: 1]}

src2: {name: 'src2', type: input, [read: 1]}

dest: {name: 'dest', type: input, [read: 1]}

regs: {name: 'regfile', type: memory, [read: 1, write: 3]}

with cycles: 3

```

TimeStep i > 0 is the state of the datapath after updating all registers and memories with the results of the  $(i-1)^{\text{th}}$  step of evaluation (because Oyster evaluates designs synchronously). op, src1, src2, and dest are all inputs in the datapath and read at time 1. regfile is a memory that maps to the set of architectural registers (regs); the datapath reads it at time 1 and writes to it at time 3. The developer also specifies how many cycles to symbolically evaluate the sketch; in this case it is equal to the depth of the pipeline.

The with clause optionally accepts a list of signals in the datapath sketch which the symbolic evaluator assumes to be true. Datapath developers provide assumptions in situations where datapath hazards interfere with architectural instruction behavior. For example, a control hazard may flush the pipeline, "killing" the currently executing instruction. In this scenario, the program synthesizer cannot find a satisfying solution for the control logic because it can always find a case where the executing instruction is invalid. Our constant-time cryptography core requires this kind of assumption in its abstraction function (Section 2.4.2).

It is possible there is no one-to-one mapping between datapath components and architectural state. For instance, an ISA specification may not distinguish between instruction memory and data memory, modeling both together, whereas a datapath targeting that ISA may choose to implement the instruction and data memories as separate memory blocks. In that case, the developer adds multiple entries to the abstraction

function, e.g., for the architectural memory example:

```

mem: {name: 'i_mem', type: memory, [read: 1]}

mem: {name: 'd_mem', type: memory, [read: 2, write: 3]}

```

In a multi-cycle design, the implementation may affect architectural state over time. Capturing these timing effects is crucial for designs with pipelining. The pipelined ALU scenario exemplifies the gap between the architectural specification and the datapath implementation. Abstraction functions bridge this gap to give our program synthesis technique enough semantic information about the relation between state in the architecture and datapath sketch to find satisfying solutions for the control logic.

### 2.3.3 Program Synthesis for Control Logic

In Figure 2.4, the process inside the dotted box illustrates the overall flow for the program synthesis step. Given a datapath sketch in an HDL, our technique first compiles the sketch into Oyster and then uses Rosette to translate the Oyster program into an SMT formula via symbolic evaluation using the theories of bitvectors and uninterpreted functions. For multi-cycle designs, the symbolic evaluator runs for the number of steps specified by the user. Then, for an architectural specification, our tool automatically extracts the pre- and postconditions and provides them as constraints to the program synthesizer. We formulate the program synthesis problem as follows:

$$\exists e_0, \ldots, e_n, \forall s_0.$$

$$\mathsf{Interpret}^k(s_0, \mathsf{Sketch}[h_0 := e_0, \ldots, h_n := e_n]) = (s_i)_{i=1}^k,$$

$$\bigwedge_{j} \mathsf{Pre}_j[s_{\mathsf{spec}} := \alpha(s_0)] \longrightarrow \mathsf{Post}_j[s_{\mathsf{spec}} := \alpha(s_1, \ldots, s_k)].$$

For all holes  $h_0, \ldots, h_n$  in the datapath sketch, the program synthesizer searches for Oyster expressions  $e_0, \ldots, e_n$ , filling the holes in Sketch with an implementation for the missing control logic. Equation (2.1) quantifies over the initial state  $s_0$  because the synthesized expressions,  $e_0, \ldots, e_n$ , must hold for *any* initial state for every instruction in the specification.

Interpret<sup>k</sup> evaluates the Oyster sketch given an initial state  $s_0$  and returns a sequence of environments,  $s_1, \ldots, s_k$ , capturing the state of the design after each step. Then, for each instruction j, the formula asserts that the precondition implies the postcondition. The precondition  $\text{Pre}_j$  takes the initial state  $s_0$  after passing through abstraction function  $\alpha$ , and the postcondition  $\text{Post}_j$  takes the computed states  $s_1, \ldots, s_k$  transformed according to  $\alpha$ .

The abstraction function  $\alpha$  acts as a substitution procedure for the pre- and post-conditions between state in the specification and state in the datapath. To understand how  $\alpha$  fits into Equation (2.1), we separate the substitution procedure into two parts, for the precondition and postcondition, respectively.

$\operatorname{Pre}_j[s_{\operatorname{spec}} := \alpha(s_0)]$ , where  $s_{\operatorname{spec}}$  is a state element from the ISA specification; read as, "for the precondition for instruction j, substitute each occurrence of  $s_{\operatorname{spec}}$  with  $\alpha(s_0)$ ."

Post<sub>j</sub>[ $s_{\text{spec}} := \alpha(s_1, \ldots, s_k)$ ], with  $\alpha(s_1, \ldots, s_k) = s_t$ , where t is a TimeStep and  $0 < t \le k$ . The substitution procedure checks whether the state element is part of a read or write using t as specified in  $\alpha$ . Further, for each *assume* in  $\alpha$ , the procedure adds a conjunction that the given datapath signal in  $s_t$  is true, where t is the associated TimeStep.

In practice, for large j (the number of instructions in the specification), solving times dramatically increase, as our evaluation shows in Section 2.5. To overcome this scalability issue, we introduce an optimization for control logic synthesis that can be applied under an assumption about the design.

#### **Optimization for Control Logic Synthesis**

To overcome the scalability limitation of the described program synthesis technique, we scale control logic synthesis by generating the control logic independently *per instruction* and then join the results together into a final overall form according to the preconditions in the specification. We introduce a property we call **instruction independence**, which must hold on the datapath sketch in order to apply this optimization. (In Section 2.3.3, we present an argument for the correctness of this optimization for the class of machines we target.)

**Instruction Independence for Control Logic** consists of two conditions that must hold on the given datapath sketch in order to solve for control logic independently:

- 1. **Mutually exclusive preconditions**: The preconditions, or antecedents, for the control logic for each instruction are disjoint.

- 2. **No feedback in control logic**: Signals output from the control logic cannot feed back into the control logic except for valid wires identified in  $\alpha$ .

For the first condition, the decoder and FSM-style control we consider in our case studies necessarily satisfy this condition, as instructions are uniquely decoded. In this way, if the control logic for two instructions share the same preconditions then the control logic is identical.

For the second condition, we require no feedback so that it is possible for the control logic to be solved independently. The exception for valid signals identified by the abstraction function allows the optimization to handle designs that have determined dependencies between instructions. For example, the constant-time cryptography core (Section 2.4.2) exhibits control hazards when branches resolve and force a flush of the currently fetched instruction. The valid signal that determines the control hazard de-

rives from the control signal controlling a branch. If there is a flush, the signal is false indicating a valid instruction is not executing, thus there is no control logic to dispatch.

The intuition for why this speeds up control logic synthesis is that specifications with large number of instructions produce correspondingly large conjunctions of constraints — following Equation (2.1) — that SMT solvers struggle to solve. By making the independence assumption about instruction behavior, we break up the conjunction. Then, our control logic synthesis tool sends the individual synthesis queries to the SMT solver which are considerably smaller.

Given an instruction in the specification, the tool extracts the instruction's preconditions (for instance, the instruction opcode as calculated by the fetch/decode logic and possibly other specified conditions, such as checking that the destination register is not the *zero* register, e.g., in RISC-V). Next, the tool extracts the specified state change as a postcondition. The result is a formula that expresses the logical statement, "assuming a specific opcode (and any other relevant preconditions), what values for the existentially quantified variables result in the asserted state change being true?" A satisfying solution from the SMT solver is a concrete bitvector assigning a value to each control signal.

Control logic synthesis repeats this process for each instruction in the specification, resulting in a mapping of control signals to concrete bitvector values. The last step is to translate this mapping into complete Oyster expressions that incorporate the constraints from all instruction semantics, producing satisfying control logic to generate each control signal based on the opcodes and other relevant state.

We call this procedure the *control union*, which we abbreviate as  $\sqcup$  and define in the algorithm in Figure 2.6. The procedure takes as input a list of holes in the datapath sketch and synthesis results from per-instruction control logic synthesis. The results variable maps for each hole the concrete bitvector value solved during control logic

```

function □(holes, results):

control := []

for hole in holes:

hole-defn := LogicGen(results[hole])

control := control + Assign(hole, hole-defn)

return control

function LogicGen(val→ops):

val, opcodes := head(val→ops)

cond := ∨ opcodes

return IfThenElse(cond, LogicGen(tail(val→ops)), val)

```

Figure 2.6: An algorithm for combining individual control logic synthesis results together into a complete implementation under the instruction independence assumption.

synthesis to an instruction (or list of instructions, if multiple instructions map to the same control signal value).

For example, consider the following map of synthesis results from a small RISC-style design with three instructions: ADD, LOAD, and JUMP; and three holes for control signals: write-register, read-memory, and jump.

```

results = {

"write-register": {0b1: [ADD, LOAD], 0b0: [JUMP]},

"read-memory": {0b1: [LOAD], 0b0: [ADD, JUMP]},

"jump": {0b1: [JUMP], 0b0: [ADD, LOAD]}}

```

After running the  $\sqcup$  procedure as described in Figure 2.6 over the results map, we obtain the following Oyster code implementing the control logic:

For readability and reuse, the variables pre-add, pre-load, and pre-jump define the preconditions for each instruction in Oyster code based on the specification (derived automatically). While this example is smaller than the control logic in our case studies, the  $\sqcup$  procedure is flexible enough to handle signals of larger bitwidths and generate nested multiplexers (through nested **if-then-else** expressions).

#### **Correctness Argument of Union Operation**

Here we argue that joining individual generated control logic per-instruction under the  $\sqcup$  procedure produces a correct implementation of control logic with respect to the architectural specification. We present our argument starting from the "ideal" problem formulation presented in Equation (2.1). By solving the control logic for each instruction individually, we rearrange the formula to:

$$\exists c_0^j, \ldots, c_n^j, \forall s_0 .$$

$$\mathsf{Interpret}^k(s_0, \mathsf{Sketch}[h_0 := c_0^j, \ldots, h_n := c_n^j]) = (s_i)_{i=1}^k,$$

$$\mathsf{Pre}_i[s_{\mathsf{spec}} := \alpha(s_0)] \longrightarrow \mathsf{Post}_i[s_{\mathsf{spec}} := \alpha(s_1, \ldots, s_k)],$$

where  $c_0^j,\dots,c_n^j$  are Oyster constants.

The new formula says that for each instruction j in the specification, there exists Oyster constants  $c_0^j,\ldots,c_n^j$  that satisfy the holes in the datapath sketch for that instruction. Applying the instruction independence assumption rearranges Equation (2.1) according to the two conditions (from Section 2.3.3). Because we assume mutually exclusive preconditions, we break the big conjunction of  $\Pr_j$  and  $\Pr_j$  into a single implication for each instruction j. Assuming no feedback in the control logic, we separate the generated control into disjoint, per-instruction pieces such that  $\lim_j c_0^j,\ldots,c_n^j\equiv e_0,\ldots,e_n$ . That is, the individual synthesis results after the control union is a correct implementation of the control logic and semantically equivalent to the Oyster expressions,  $e_0,\ldots,e_n$ , generated from Equation (2.1). As the full formula is a conjunction of all predicates  $\Pr_j$  and  $\Pr_j$  for each instruction j, we break each expression  $e_i$  filled for hole  $h_i$  into per-instruction pieces such that  $\lim_j c_j^j \equiv e_i$ .

Note that this correctness argument does not necessarily hold for designs that do not make this assumption or are outside of the class of machines we consider in this work. In Section 2.5.3, we discuss the limitations of the instruction-independence assumption and highlight future work to support more kinds of microarchitectures.

## 2.4 Case Studies

Here we cover three case studies: (1) an embedded-class RISC-V core, (2) a bespoke RISC-V core with a custom instruction set for constant-time cryptography, and (3) a cryptographic accelerator targeting AES. For each, we show how we specialize the core flow of our technique from Section 2.3.

Through these case studies, we emulate an "agile" design flow. The case studies start with a base datapath sketch and off-the-shelf ILA specification, where we demonstrate the control logic synthesis technique. Then, we modify either the specification

or the datapath, or both, and show how control logic synthesis can again be invoked to automatically re-generate the control logic given the design changes.

#### 2.4.1 Embedded-Class RISC-V Core

In this case study, we demonstrate how our control logic synthesis technique automatically generates the implementation of the instruction decoder-style control logic for different iterations of an embedded-class RISC-V core. We use an existing ILA specification for the RISC-V ISA [28]. The case study iterates on the design over two dimensions—modifying the architectural specification by adding ISA extensions, and modifying the datapath sketch by adding a pipeline.

We begin with the RISC-V 32-bit integer base instruction set (RV32I). This set totals 37 instructions, excluding the ecall and ebreak instructions because the target cores do not implement exceptions or interrupts. Then we add to the base ISA two extensions geared towards cryptography: Zbkb and Zbkc. The Zbkb extension is a set of 12 bit-manipulation instructions which are common in cryptographic applications: rotate (rol, ror, rori), logical-with-negate (andn, orn, xnor), byte reversal (rev8, rev.b), shuffle (zip, unzip), and word packing (pack, packh). Zbkc is an extension that adds two carryless multiply instructions: clmul and clmulh.

#### Single-Cycle Datapath

We start with a single-cycle datapath sketch, implementing the main components of the processor for executing each instruction class. To write the sketch, the developer identifies control points in the datapath and leaves these as holes, following the instruction-decoder pattern for control logic (described in Section 2.2.2). The following shows a portion of the datapath sketch in PyRTL, underlining the control signal

#### variables for emphasis:

```

instruction = fetch(i_mem, pc)

opcode, funct3, funct7, imm = decode(instruction)

alu_imm <<= ??(opcode, funct3, funct7)</pre>

alu_op

<= ??(opcode, funct3, funct7)

reg_write <<= ??(opcode, funct3, funct7)</pre>

read_mem <<= ??(opcode, funct3, funct7)</pre>

<= ??(opcode, funct3, funct7)

jump

alu_in2 <<= mux(alu_imm, rs2_val, imm)</pre>

alu_out <<= alu(alu_op, rs1_val, alu_in2)</pre>

# Register file update

with conditional_assignment:

with reg_write:

with read_mem:

rf[rd] |= d_mem[alu_out]

with jump:

rf[rd] \mid = pc + 4

with otherwise:

rf[rd] |= alu_out

# PC update

pc.next <<= mux(jump, pc + 4, target)</pre>

```

For each signal, the developer leaves its implementation as a hole (??) and passes as input the parts of the decoded instruction (opcode, funct3, and funct7).

**Abstraction Function** The microarchitecture of the single-cycle core closely matches

the architectural specification. There is no special timing and state effect information to consider; all reads and writes happen at time step 1:

```

pc: {name: 'pc', type: register, [read: 1, write: 1]}

GPR: {name: 'rf', type: memory, [read: 1, write: 1]}

mem: {name: 'd_mem', type: memory, [read: 1, write: 1]}

mem: {name: 'i_mem', type: memory, [read: 1]}

with cycles: 1

```

In the ILA specification for RISC-V, GPR stands for "general-purpose registers" and is modeled as a vector of registers. In the datapath sketch, GPR maps to a memory rf which is the register file. The datapath sketch also separates instruction and data memory as i\_mem and d\_mem, respectively.

**Program Synthesis** As our results show in Section 2.5, the program synthesis tool is unable to generate control logic for the entire core ISA specification at once. To overcome this limitation, we take advantage of the RISC-V ISA instruction independence (i.e., the control logic for each instruction does not depend on any other instructions) and apply the optimization described in Section 2.3.3, generating control logic for each instruction independently and combining them together according to the algorithm in Figure 2.6.

Figure 2.7 shows an example of the generated control logic in PyRTL for a load word instruction (LW) from the RISC-V core. The with statements in PyRTL specify conditional assignments for wire variables in the design (with the conditional assignment operator denoted by |=). The code in Figure 2.7 executes control logic for a LW instruction because the conditional with expressions match on the corresponding opcode and 3-bit function code from the decoded instruction. For a load instruction, control logic synthesis determines that the following must occur in the datapath to satisfy the ISA

instruction semantics for LW:

- Signal a memory read (mem\_read |= 1) with the mask for a word-sized load (mask\_mode |= 2).

- Perform an ALU operation with the operation signaled by alu\_op |= ADD, and direct the immediate value from the decoded instruction into one of the ALU's inputs (alu\_imm |= 1). These control signals coordinate the calculation of the address to be read from memory.

- Signal a write to the register file (reg\_write |= 1).

- Set other control signals to *false* so that other state elements are not modified in a way that is inconsistent with the ISA instruction semantics (e.g., mem\_write, and jump are all set to 0).

#### Two-Stage Pipeline Datapath

Next, we extend the design to an embedded-class core similar to Ibex [29]. We keep the ISA specification (including extensions) exactly the same as the single-cycle core, and only change the datapath sketch, adding two pipeline stages. The first pipeline stage is instruction fetch, decode and execute. The second pipeline stage is memory and write back.

**Abstraction Function** Because we introduce pipelining into the datapath, we need to strengthen the abstraction function by adding timing information related to the microarchitecture. Specifically, we indicate for each corresponding architectural state element in the datapath which cycle (i.e., pipeline stage) that state is read or modified.

```

with op == LOAD:

with funct3 == 0x2:

mem_read |= 1

mask_mode |= 2

alu_op |= ADD

alu_imm |= 1

reg_write |= 1

mem_write |= 0

mem_sign_ext |= 0

jump |= 0

# Other control signals continue...

```

Figure 2.7: PyRTL code of the generated control logic for a load word instruction (LW) in the RV32I core. LOAD and ADD are mnemonics for numeric values and used here for readability. The with construct in PyRTL is syntactic sugar for nested multiplexers which we present here for readability.

Due to pipelining, without this timing information the generated pre- and postconditions will not have semantically valid values and the program synthesizer will fail to find a satisfying implementation for the control logic.

```

pc: {name: 'pc', type: register, [read: 1, write: 2]}

GPR: {name: 'rf', type: memory, [read: 1, write: 2]}

mem: {name: 'd_mem', type: memory, [read: 2, write: 2]}

mem: {name: 'i_mem', type: memory, [read: 1]}

with cycles: 2

```

The main changes to the abstraction function from the single-cycle core are the read and write time steps (underlined). In the two-stage pipeline, reads and writes to the register file occur in parallel (stage 1 and stage 2). All data memory operations occur in

stage 2. By indicating a read at time step 1 (i.e., stage 1 of the pipeline), any writes that occurred in parallel in stage two will be available from the perspective of the symbolic evaluator.

**Program Synthesis** With the new abstraction function, program synthesis follows the same as the single-cycle core, except the symbolic evaluator runs the sketch for 2 cycles.

## 2.4.2 Constant-Time Cryptography Core

As an additional case study, we modify the RISC-V design described above to create a bespoke core for constant-time cryptography. The motivation is that conditional branch instructions introduce variable instruction latency, which reveal timing side channels. We modify the RISC-V ISA specification to remove conditional branch instructions and all other instructions not necessary to execute SHA-256. We then extend it with a custom instruction for conditional move (CMOV). In cryptographic deployments, this bespoke instruction set ensures that the number of cycles executed on the core remains independent of the input length, making it resilient to timing side channel attacks.

Starting from the two-stage RISC-V core, we modify the datapath to add a third pipeline stage, remove all conditional branching logic, and extend the decode unit and ALU to support the new CMOV instruction. The three stages are: (1) instruction fetch, (2) instruction decode and execute, and (3) memory and write back.

**Abstraction Function** The abstraction function for the three-stage pipeline is a modification of the two-stage abstraction function, following the read and write timing of the new datapath.

```

pc: {name: 'pc', type: register, [read: 1, write: 2]}

GPR: {name: 'rf', type: memory, [read: 2, write: 3]}

mem: {name: 'd_mem', type: memory, [read: 3, write: 3]}

mem: {name: 'i_mem', type: memory, [read: 1]}

with cycles: 3, [instruction_valid: 1]

```

The main change is the instruction\_valid signal assumption in the datapath. The assumption states that this wire should be true at time step 1. This assumption resolves the case when there is a control hazard in the pipeline. An unconditional branch instruction such as JAL will resolve in stage 2, and force a flush of the fetched instruction in stage 1. Assuming instruction\_valid is true will prevent the solver from trying to synthesize control for an instruction that is going to be flushed.

**Program Synthesis** The program synthesis step requires no change from the previous case studies; symbolic evaluation runs for 3 cycles.

#### 2.4.3 AES Hardware Accelerator

In this case study, we demonstrate how our control logic synthesis technique automatically generates the implementation of the FSM-style control logic for an AES-128 hardware accelerator. We take an existing ILA specification for AES-128 encryption [28], and compile it to constraints for our control logic synthesis tool as described in Section 2.5.1. While the AES specification does not have typical "instructions" as a general-purpose ISA does, it splits the main computation units for AES encryption into three distinct states: "first", "intermediate", and "final". The ILA models each state as a separate ILA instruction, which the device can exist in for one or more "rounds." As an example, the following code is part of the ILA specification for the intermediate round AES computation (functions CipherUpdate\_MidRound and KeyUpdate\_MidRound

compute the update for their respective state elements):

```

auto instr = model.NewInstr("IntermediateRound");

instr.SetDecode((round > 0) & (round < 9));

instr.SetUpdate(round, round + 1);

instr.SetUpdate(ciphertext,

CipherUpdate_MidRound(ciphertext, round, round_key));

instr.SetUpdate(round_key,

KeyUpdate_MidRound(round_key, round));</pre>

```

The two key components are SetDecode and SetUpdate. The SetDecode function specifies the preconditions for the device existing in that state. The SetUpdate function specifies the postconditions, that is, the associated updates for state elements ciphertext, round\_key, and round.

For the datapath sketch we implement a multi-cycle datapath for the AES accelerator following an FSM-style control structure. The datapath computes one round of encryption at a time, keeping track of the rounds between cycles. We leave holes for computing the state transition logic as well as holes for the states themselves (in the with expressions).

```

state <<= ??

with conditional_assignment:

with state == ??:

# Computation for first round ...

with state == ??:

# Computation for intermediate rounds ...

with state == ??:

# Computation for final round ...</pre>

```

The datapath describes how the hardware computes with and modifies the archi-

tecture level state such as round\_key and ciphertext, but it does not describe what the states are or how the states transition between each other.

**Abstraction Function** The abstraction function bridges the gap between the AES specification and the datapath sketch by explicitly mapping the inputs and registers in the datapath sketch to the architectural elements in the specification. This design is not pipelined so we do not capture any timing-related information in the datapath.

**Program Synthesis** The result of control logic synthesis for AES fills in state condition and state transition logic for the FSM, and generates the state encodings.

```

state <<= mux(round == 0,

mux((round > 1) & (round <= 9), 0b10, 0b01), 0b00)

with conditional_assignment:

with state == 0b00:

# Computation for first round ...

with state == 0b01:

# Computation for intermediate rounds ...

with state == 0b10:

# Computation for final round ...</pre>

```

We note that we did not make any changes to the core control logic synthesis technique to support the AES hardware accelerator. The developer follows the same procedure, providing a datapath sketch and ILA specification. This case study demonstrates the generality of our technique and shows promise for applying control logic synthesis to the development of hardware accelerators in other domains such as image processing, AI, and machine learning, as well as other aspects of SoC design such as protocol implementations (for example, cache coherence protocols) [30].

#### 2.5 Evaluation

In this section, we present the results of control logic synthesis over all designs from our case studies. We ran all experiments on a workstation running Ubuntu 20.04 GNU/Linux (kernel version 5.15) with an Intel Xeon Gold 6226R 3.9 GHz processor and 96 GB RAM.

## 2.5.1 Implementation

Our implementation spans several languages for each major component in the tool flow. Overall, the Racket code implementing the Oyster interpreter and program synthesis procedures are just over 1,000 source lines of code (SLOC). Translating PyRTL to Oyster is about 150 SLOC of Python. Our implementation also includes adding support for holes in the PyRTL language. With the exception of the bespoke cryptography core, we use unmodified, off-the-shelf ILA specifications for all of the case studies.

The ILA to Rosette compiler is 550 SLOC of C++. Figure 2.8 presents a grammar that defines the compilation process. Bold names in the grammar correspond to ILA intrinsic functions that model common bit manipulation and comparison operations whereas bold names in the translation function correspond to Rosette functions.

```

DecodeExpr ::= SetDecode(expr)

UpdateExpr ::= SetUpdate(state_var, expr)

expr ::= sym \mid expr \ binop \ expr \mid !expr

| Extract(expr, int, int)

| Load(expr, expr) | Load(expr)

| Concat(expr, expr)

| Ite(bool_expr, expr, expr)

| ZExt(expr, int)

binop ::= + | == | & | ...

\mathsf{sym} \ ::= int \mid state\_var \mid input\_var

T[DecodeExpr] ::= (assume T[expr])

T\llbracket UpdateExpr

Vert ::= (assert (bveq <math>T\llbracket expr

Vert (astate\_var))))

T[\![expr]\!] ::= (\mathbf{bvnot} \ T[\![expr]\!])

T[\mathbf{Extract}(expr, int, int)] ::= (\mathbf{extract} \ T[expr]] \ int \ int)

T[[Load(expr, expr)]] ::= (read-mem(pre(\alpha T[[expr]])) (bv T[[expr]] addr_width))

T[[Load(expr)]] ::= (pre (\alpha T[[expr]]))

T[Concat(expr, expr)] ::= (concat T[expr] T[expr])

T[\text{Ite}(expr, expr, expr)] ::= (\text{if } T[expr] T[expr] T[expr])

T[\mathbf{ZExt}(expr, int)] ::= (\mathbf{zero-extend} \ T[expr]] \quad (\mathbf{bitvector} \ int))

T[+] ::= \mathbf{bvadd} \quad T[==] ::= \mathbf{bveq}

T[\&] ::= bvand \dots

```

Figure 2.8: The grammar for ILA decode and update expressions with their Rosette transformation rules. T[] defines the translation function. **pre** is the initial state environment. **post** is the sequence of environments produced after symbolic evaluation (dependent on the number of steps).  $\alpha$  is the abstraction function.

The DecodeExpr and UpdateExpr are the top-level rules that are translated into assume and assert statements in Rosette, respectively. An ILA-modeled instruction is valid if the expr argument is true. A modeled instruction may also update one or more state variables with a call to SetUpdate and passing the variable as well as the new value. Translation proceeds by syntactically rewriting the rest of the expression tree.